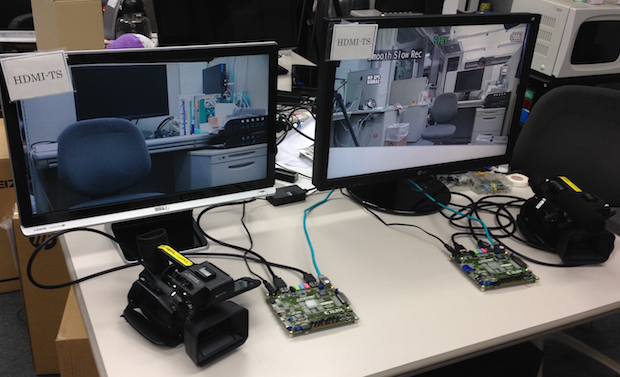

自作HMD(ヘッドマウントディスプレイ)を用いた低遅延ロボット(ダンボーくん)操作環境を展示します。私達は過去に、FPGAを用いてHDMIカメラ入力を直接Ethernetに変換することで、超低遅延な遠隔カメラ回路を作成しました。今回の展示は、ダンボール型ロボットの目にそれぞれカメラを埋め込み、ダンボーくんの遠隔首振りが可能なVRロボットアバターを展示します。[PROFILE]慶應義塾大学村井研究室内のFPGA同好会。研究の傍ら、デジタル回路などを勉強し、FPGAを用いたネットワーク機器やIPによる映像伝送技術の設計もしています。また、私達は、Digilent Design Contest 2014の日本大会でIPによる低遅延映像伝送機器の設計で優勝を収めています。